2023年3月22日,北京大学化学与分子工程学院彭海琳教授课题组在《自然》(Nature)期刊上发表题为“2D fin field-effect transistors integrated with epitaxial high-κ gate oxide”的研究论文。该研究报道了世界首例二维半导体鳍片/高κ栅氧化物异质结阵列的外延生长及其三维架构的异质集成,并研制了高性能二维鳍式场效应晶体管(2D FinFET)。外延制备的二维半导体鳍片/单晶高κ自氧化物异质结(2Dfin/oxideBi2O2Se/Bi2SeO5)具有原子级平整界面和超薄的鳍片厚度(达一个单胞厚度,~1.2纳米),可实现晶圆级定向阵列制备和定点、高密度生长。基于Bi2O2Se/Bi2SeO5外延异质结的二维鳍式场效应晶体管具有很高的电子迁移率,极低的关态电流,很大的开/关态电流比和开态电流密度,满足国际器件与系统路线图(IRDS)的2028年低功耗器件目标要求。该原创性工作突破了后摩尔时代高速低功耗芯片的二维新材料精准合成与新架构三维异质集成瓶颈,为开发未来先进芯片技术带来新机遇。

集成电路作为信息社会的基石,正朝着高性能、低功耗、多样性和高集成度方向发展。以传统硅基半导体/氧化物(如Si/SiO2、Si/HfO2)为核心的CMOS(互补金属氧化物半导体)晶体管通过器件尺寸的持续微缩维持芯片迭代的需求。目前硅基芯片已成功迭代至5纳米制程节点。随着摩尔定律推进并逼近物理极限,传统硅基半导体材料在芯片尺寸微缩极限下遇到短沟道效应等关键挑战,功耗上升和算力不足等瓶颈问题日益突出。探索“后摩尔时代”新材料、新器件和新架构,有望突破芯片功耗和算力瓶颈,推动高端电子器件与集成电路芯片的可持续发展。

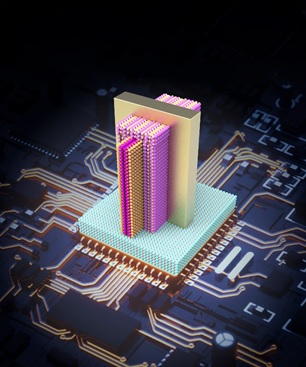

材料与架构的创新是集成电路过去30多年来发展的核心驱动力。1998年,芯片的铜金属互联技术助力突破了180纳米节点;2003年,硅锗掺杂形成迁移率更高的应力硅,助力突破了90纳米节点并降低了能耗;2007年,高介电常数(κ)氧化物栅介质HfO2取代传统二氧化硅和氧氮化硅栅介质,同时金属栅代替了多晶硅栅,HKMG(High-κ Metal Gate)工艺技术得到成功应用,突破了45纳米节点;2011年,以垂直鳍片(Fin)硅基沟道架构和三栅极围绕结构的鳍式场效应晶体管(FinFET)技术实现商业化量产,并应用于22纳米制程工艺,从此主导了现代晶体管微缩制程工艺,也是当前最先进的商用5纳米制程集成电路的主流架构。材料和架构的持续创新是摩尔定律推进的重要基础,但每项改进都伴随着权衡与取舍。当前技术节点正进入亚3纳米,二维半导体因其具有表面无悬挂键、原子级厚度和高迁移率等特性,可有效抑制硅基器件微缩极限下的短沟道效应,并实现出色的栅控和高驱动电流,可作为“后硅材料”延续CMOS器件微缩,提高芯片集成度和算力。为此,由学术界、产业界共同制定的国际器件与系统路线图(IRDS)已将二维半导体作为替代硅的备选材料之一。在全球工业界,芯片研发和制造龙头公司如英特尔、台积电、三星及IMEC等是二维材料应用于集成电路芯片的主要推动者,已经布局了产业先导研究。与此同时,垂直鳍片沟道架构的新器件开发仍备受关注,业界正在考虑制造基于垂直鳍式结构开发围栅器件(GAA)、垂直围栅器件(VGAA)或垂直传输场效应晶体管(VTFET),以满足“后摩尔时代”芯片的更高集成度、高性能和低功耗发展要求。

后摩尔时代的晶体管尺寸持续微缩亟需芯片关键材料及其三维异质集成技术的创新。开发全新架构的高迁移率二维层状半导体垂直鳍片/高κ氧化物异质集成技术,构筑二维鳍式场效应晶体管(2D FinFET)等新架构器件(图1),有望突破传统硅基晶体管物理极限,具有重要意义。2D FinFET中二维半导体鳍片和三栅极环绕结构的异质集成,增加了沟道栅控面积,增强器件栅控能力,有效抑制短沟道效应,并降低亚阈值漏电流,有望进一步突破芯片算力、能效和集成瓶颈(图2)。然而,新型高迁移率二维半导体鳍片和高κ氧化物异质结的精准制备及三维异质集成等关键科学问题亟待解决。

图1. 外延高κ栅氧化物集成型二维鳍式晶体管(2D FinFET)示意图

北京大学彭海琳教授课题组长期从事二维材料物理化学与表界面调控研究,致力于解决新型高迁移率二维材料(石墨烯、铋基硫氧族材料BOX等)的表界面生长控制及结构与性能调控中具有挑战性的国际前沿科学问题,前期创制了全新高迁移率二维半导体芯片材料Bi2O2Se(NatureNanotech.2017,12,530;Acc. Mater. Res. 2021,2, 842),开发了二维半导体Bi2O2Se的超薄高κ自然氧化物栅介质Bi2SeO5及高性能二维晶体管(NatureElectron.2020,3,473;Nature Electron. 2022,5, 643;Nature Mater. 2023)。近期,该研究团队致力于将高迁移率二维半导体与高κ栅介质精准集成并极限微缩成三维新架构。

针对二维沟道材料与介电质精准合成及其三维架构异质集成这一难题,最近,北京大学彭海琳教授课题组独辟蹊径,建立了绝缘基底上晶圆级二维半导体Bi2O2Se垂直鳍片阵列的外延生长方法,并利用可控氧化方法,实现了二维Bi2O2Se鳍片/高κ自氧化物Bi2SeO5异质结的外延集成(图3)。值得强调的是,二维Bi2O2Se表面可被逐层可控插层氧化减薄至1个单胞厚度(1.2纳米),并与高κ表面单晶氧化层Bi2SeO5形成原子级平整、晶格匹配的高质量半导体/介电层界面。结合微纳加工及可控刻蚀技术,精确控制二维鳍片的成核位点与生长过程,实现了单一取向的二维垂直鳍片/高κ自氧化物异质结阵列的定点和定向外延。并在此基础上实现了沟道厚度约6纳米的高性能二维鳍式晶体管(2D FinFET)的研制。新型二维半导体沟道/外延集成高κ栅介质基二维鳍式晶体管在迁移率(270 cm2/Vs)、关态电流(1 pA/μm)和电流开关比(108)等性能满足业界高性能低功耗器件要求。在开态电流密度方面,相对于商用硅、锗及二维过渡金属硫化物(TMD)等材料,Bi2O2Se/Bi2SeO5二维鳍式晶体管也展现出电子学上的优势和潜力。

图2. 二维晶体管在未来CMOS芯片微缩中的发展潜力

图3.二维半导体鳍片/高κ氧化物异质结外延集成及高性能二维鳍式晶体管(2D FinFET)。(a)高迁移率二维半导体Bi2O2Se鳍片/高κ自氧化物Bi2SeO5异质外延集成示意图;(b)单一取向二维半导体鳍片/外延氧化物异质结的扫描电镜表征形貌图;(c)晶圆级二维半导体鳍片/外延氧化物异质结阵列的光学照片;(d)二维半导体鳍片/外延氧化物异质结构截面高分辨透射电子显微镜成像;(e)高性能二维鳍式晶体管(2D FinFET)与商用Si、Ge及过渡金属硫化物(TMD)等沟道材料器件电学性能(开态电流密度)对比。

该项研究在国际上首次实现了一类全新架构的高迁移率二维半导体鳍片/高κ氧化物外延异质结的精准合成与集成,并研制了高性能二维鳍式场效应晶体管(2D FinFET)。该原创性工作突破了后摩尔时代高速低功耗芯片的二维新材料精准合成与新架构三维异质集成瓶颈,构筑了高性能的晶体管器件,为开发未来高性能芯片技术提供了全新的思路。

该研究成果以“外延高κ栅氧化物集成型二维鳍式晶体管”(2D fin field-effect transistors integrated with epitaxial high-κ gate oxide)为题,近日发表于国际顶级学术期刊Nature。北京大学化学与分子工程学院彭海琳教授是该论文工作的通讯作者,北京大学化学与分子工程学院BMS Fellow博士后谭聪伟、博士研究生于梦诗、唐浚川、高啸寅是共同第一作者。生长理论计算和形貌表征方面的主要合作者还包括韩国蔚山国立科技研究院丁峰教授、清华大学物理系姜开利教授等。该研究成果得到国家自然科学基金委、科技部、北京分子科学国家研究中心、腾讯基金会、北京大学博雅博士后、北京分子科学国家研究中心博士后项目等机构和项目的资助,并得到了北京大学化学与分子工程学院的分子材料与纳米加工实验室(MMNL)仪器平台的支持。

论文链接:https://www.nature.com/articles/s41586-023-05797-z