在人工智能(AI)时代,传统冯·诺依曼计算架构因存储与计算单元物理分离,导致芯片算力与能效提升面临显著瓶颈。铁电材料凭借其自发极化及极化方向可快速切换的特性,能够实现非易失性存储与高能效矩阵计算,成为构建存算一体非冯·诺依曼架构、突破传统“功耗墙”与“存储墙”限制的关键方案之一。然而,铁电氧化物薄膜材料在实际应用中仍面临大面积均匀制备困难、铁电性能随厚度微缩而衰退等问题,尤其在向亚5纳米先进工艺节点微缩时,这些挑战更加突出,严重制约了先进计算架构的发展与高能效芯片的实现。

2026年1月29日,北京大学化学与分子工程学院彭海琳教授研究团队在《科学》(Science)在线发表了题为《晶圆级超薄且均匀的范德华铁电氧化物》“Wafer-scale ultrathin and uniform van der Waals ferroelectric oxide”的研究长文(Science 2026, 391, eadz1655.DOI: 10.1126/science.adz1655),报道了一种新型高介电常数(κ)范德华铁电材料α-硒酸铋( Bi2SeO5 ),成功实现了后道工艺兼容的晶圆级超薄均匀铁电薄膜制备。针对铁电层与半导体沟道层异质界面易受损的难题,该工作基于研究团队自主开发的高迁移率铋基二维半导体 Bi2O2Se 晶圆材料,建立了精准可控的自氧化制备方法,首次制备出具有原子级平整界面和超薄铁电层(单晶胞厚度,~1纳米)的晶圆级铁电/半导体异质结构,并构筑了工作电压超低(0.8 V)、耐久性极高(1.5×1012次循环)的高速铁电晶体管,其综合性能全面超越了现有工业级铪基铁电体系。并成功构建出可动态重构的存内逻辑运算电路,在CMOS常规低电压下(<1 V)即可实现可切换的逻辑功能。该类器件是目前已知工作电压最小、能耗最低且耐久性最优的铁电晶体管,标志着二维铁电器件性能达到了新的高度。此项成果构建了全球首个晶圆级二维铁电材料体系,突破了后摩尔时代非冯·诺依曼架构芯片在新材料合成与异质集成方面的关键技术瓶颈。

该研究不仅可应对“超越摩尔定律”路线下新型计算架构与大规模神经形态计算系统在可扩展性、可靠性和三维集成等方面的多重挑战,更为开发高能效先进芯片提供了突破性材料基础与技术路径,有望推动人工智能硬件向更高算力、更低功耗的方向持续发展。

图1. 晶圆级范德华高 κ 铁电氧化物/高迁移率二维半导体异质结及其高性能铁电晶体管器件示意图。

产业背景:AI时代芯片算力与功耗的双重挑战

AI、云计算、大数据、5G等技术的快速发展持续推升对芯片性能的需求。然而,传统硅基芯片的发展已步入发展瓶颈:尺寸微缩逐渐逼近物理极限,短沟道效应、量子隧穿等问题不断凸显,摩尔定律(Moore’s law)的演进速度明显放缓。更为关键的是,沿用数十年的冯·诺依曼架构由于计算与存储单元分离,数据在两者之间频繁搬运,形成巨大的能耗与延迟,即所谓的“功耗墙”与“存储墙”,严重制约系统整体能效的提升。为打开这一僵局,必须发展“超越摩尔定律”的新技术路线,着力于新材料、新器件与新架构的研发与突破,来重新定义芯片的未来。

关键瓶颈:高品质铁电材料的制备困境

1920年,铁电现象在实验中被意外发现。在百年发展历程中,关于铁电材料的基础研究和应用探索层出不穷。在众多前沿技术路径中,铁电材料凭借其独特的“自发极化”特性备受关注,近年来被视为构建下一代非冯·诺依曼架构存算一体芯片的关键候选。这种材料在外加电场下快速可逆切换极化状态,并能在断电后长期保持,实现对数据的非易失存储,其功能类似具备“记忆”能力。铁电晶体管( FeFET )具有简单紧凑的三端器件结构,将“只算不存”的场效应晶体管中的高κ栅介质,变更为铁电栅介质,巧妙利用铁电材料的可快速电场调控的极化双稳态与非易失性存储特征,将存储和计算功能完美融合在单一器件中,从根本上消除数据搬运,突破“功耗墙”与“存储墙”限制,兼具高密度、高速度和低功耗特点,非常适用于存算一体、神经形态计算等先进领域。

然而,从理想到现实的道路充满挑战。要将铁电材料推向产业化,必须解决一个关键瓶颈:如何实现高品质铁电薄膜的可靠制备。当前,氧化铪(HfO2)基铁电材料因与现有硅基工艺兼容性较好,已成为主流体系。然而在向晶圆级、超薄化发展时,铪基铁电材料仍面临均匀性不足、界面退极化效应显著、厚度低于5纳米时铁电性能急剧衰退等问题。其根源在于薄膜中多相共存、结构缺陷、晶粒不均匀等深层材料难题。可以说,制备出大面积均匀、仅数原子层厚且具有稳定铁电性的“完美薄膜”极具挑战。

因此,在芯片工艺节点持续微缩的背景下,人们不仅需要优化现有铁电材料体系,更亟需探索兼具晶圆级均匀性、超薄稳定铁电特性,且与现有半导体工艺高度兼容的新型铁电材料。唯有跨越这一材料瓶颈,才能真正释放铁电器件的潜力,推动高集成、低功耗的存算一体芯片从实验室走向规模化应用。

视频:晶圆级超薄均匀铁电薄膜α-Bi2SeO5及铁电晶体管

材料创新:兼具晶圆级制备、超薄特性与均匀性的新型铋基二维高κ铁电氧化物体系

北京大学彭海琳课题组长期致力于面向芯片应用的二维材料物理化学研究,聚焦于发展“后摩尔时代”的二维电子材料与器件。2017年,课题组发现并制备出一种新型超高迁移率二维铋基半导体硒氧化铋(Bi2O2Se),其迁移率(~450 cm2 V−1 s−1)显著优于硅及其他二维半导体材料,并具有优异的热稳定性和空气稳定性,从而奠定了铋基二维半导体材料体系的基础(Nature Nanotech. 2017, 12, 530)。随后,课题组进一步发现Bi2O2Se可氧化形成两种原生高κ氧化物α-Bi2SeO5与β-Bi2SeO5。该体系是目前除硅基体系以外,少有的具有高界面质量的原生介电层/半导体异质结材料体系,高达21的高介电常数支持构筑等效氧化层厚度为亚1纳米乃至亚0.5纳米的超低功耗晶体管(Nature Electron. 2020, 3, 473; Nature Electron. 2022, 5, 643)。基于该铋基二维半导体/高κ氧化物体系,课题组持续推进后摩尔先进架构器件,先后成功制备出全球首例外延高κ栅介质集成的二维鳍式晶体管(Nature 2023, 616, 66)与二维环栅晶体管(Nature Mater. 2025, 24, 519),并实现了在工业衬底上外延制备可转移的二维环栅单晶晶圆(Nature Commun. 2025, 16, 10857)。这些突破性进展攻克了二维电子学发展的关键科学瓶颈,为开发高性能芯片技术提供了全新路径。此外,依托该材料体系,课题组还研制了一系列高性能器件,包括二维晶体管、红外探测器、传感器以及量子霍尔器件(Nature Commun. 2018, 9, 3311; Nature Mater. 2023, 22, 832; Nature Nanotech. 2024, 19, 1452; Phy. Rev. Lett. 2025, 135, 246302),展现了该铋基二维材料体系在多功能电子与光电器件方面的广泛潜力。

为突破传统芯片架构所面临的“功耗墙”和“存储墙”制约,课题组近年来一直致力于适用于非冯·诺依曼架构先进芯片的新材料体系。早在2018年,课题组便率先发现铋基二维半导体Bi2O2Se的原生层状高κ氧化物栅介质α-Bi2SeO5,并通过理论计算预测其可能具有铁电性。然而,从理论推测到实验证实,却是一条充满挑战的漫漫长路。受限于材料制备、器件加工与表征技术等多重瓶颈,该推测迟迟未能获得实验支撑。

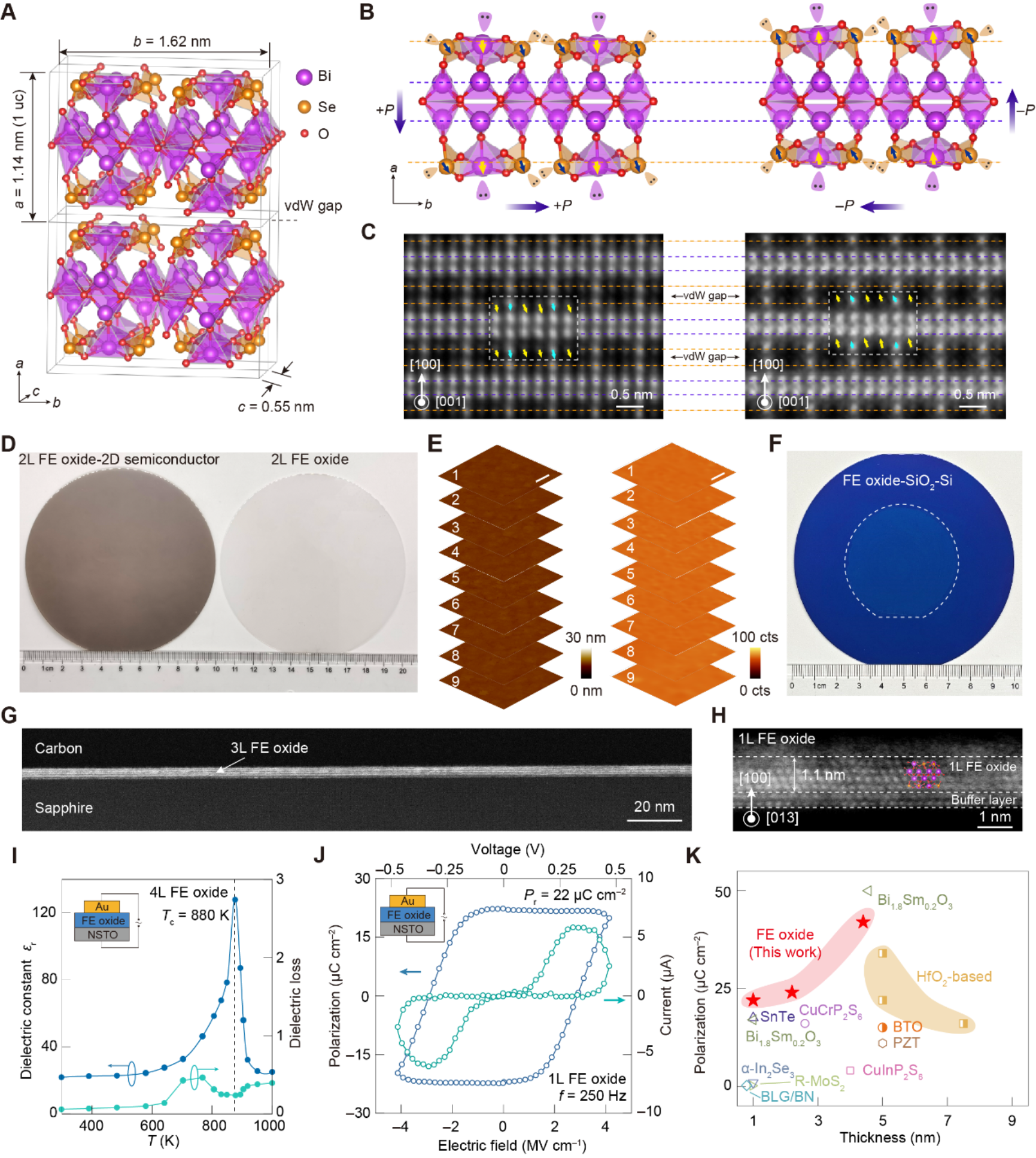

科研突破往往源于持续深耕。经过近八年的不懈探索,课题组不仅首次在实验上确证了α-Bi2SeO5具有稳定的铁电性,更建立了一套后道工艺兼容(≤400 °C)的原位氧化制备方法,成功实现了层状α-Bi2SeO5超薄铁电薄膜的晶圆级均匀制备(图1)。该方法以钛酸锶或蓝宝石衬底上化学气相沉积(CVD)生长的高迁移率二维半导体Bi2O2Se薄膜为基础,通过精确可控的逐层氧化,构筑出具有原子级平整锐利界面的α-Bi2SeO5/Bi2O2Se 二维铁电/半导体异质结构,进一步氧化获得纯相α-Bi2SeO5薄膜。值得关注的是,凭借其独特的范德华层状结构,α-Bi2SeO5即使薄至单层(约1纳米),仍能保持稳定的面外与面内耦合铁电性,并表现出适中的矫顽场(约2.5 MV cm−1)以及高达约22 μC cm−2的剩余极化强度。此外,α-Bi2SeO5具备高达24的介电常数以及超过880 K的居里温度,预示着其在低功耗与高温等极端环境应用的巨大潜力。

尤其重要的是,单层厚度下仍能维持宏观铁电极化,证明层状α-Bi2SeO5无临界尺寸限制,且具备优异的抗退极化场能力。这使其成为实现原子级厚度非易失存储器及亚5纳米三维存算一体架构的理想材料候选,为突破现有芯片性能边界打开了全新可能。

图2. 二维高κ铁电氧化物 α-Bi2SeO5 的晶圆级均匀制备及铁电性。(A)α-Bi2SeO5 的范德华层状晶体结构;(B)α-Bi2SeO5 的铁电极化态示意图;(C)α-Bi2SeO5 的铁电两个不同极化态的透射电镜图像;(D)晶圆级α-Bi2SeO5/Bi2O2Se 二维铁电/半导体异质结构及α-Bi2SeO5 铁电薄膜;(E)α-Bi2SeO5 铁电薄膜晶圆的均一性统计;(F)转移到硅衬底上的 α-Bi2SeO5 铁电薄膜晶圆;(G)大范围均匀的 α-Bi2SeO5 铁电薄膜透射电镜图像;(H)单层 α-Bi2SeO5 铁电薄膜的透射电镜图像;(I)α-Bi2SeO5 的介电常数及相变温度;(J)单层 α-Bi2SeO5 的P-E电滞回线;(K) α-Bi2SeO5 与其他铁电材料体系的厚度及剩余极化强度对比。

器件突破:超低工作电压、高耐久的二维铁电晶体管及电路

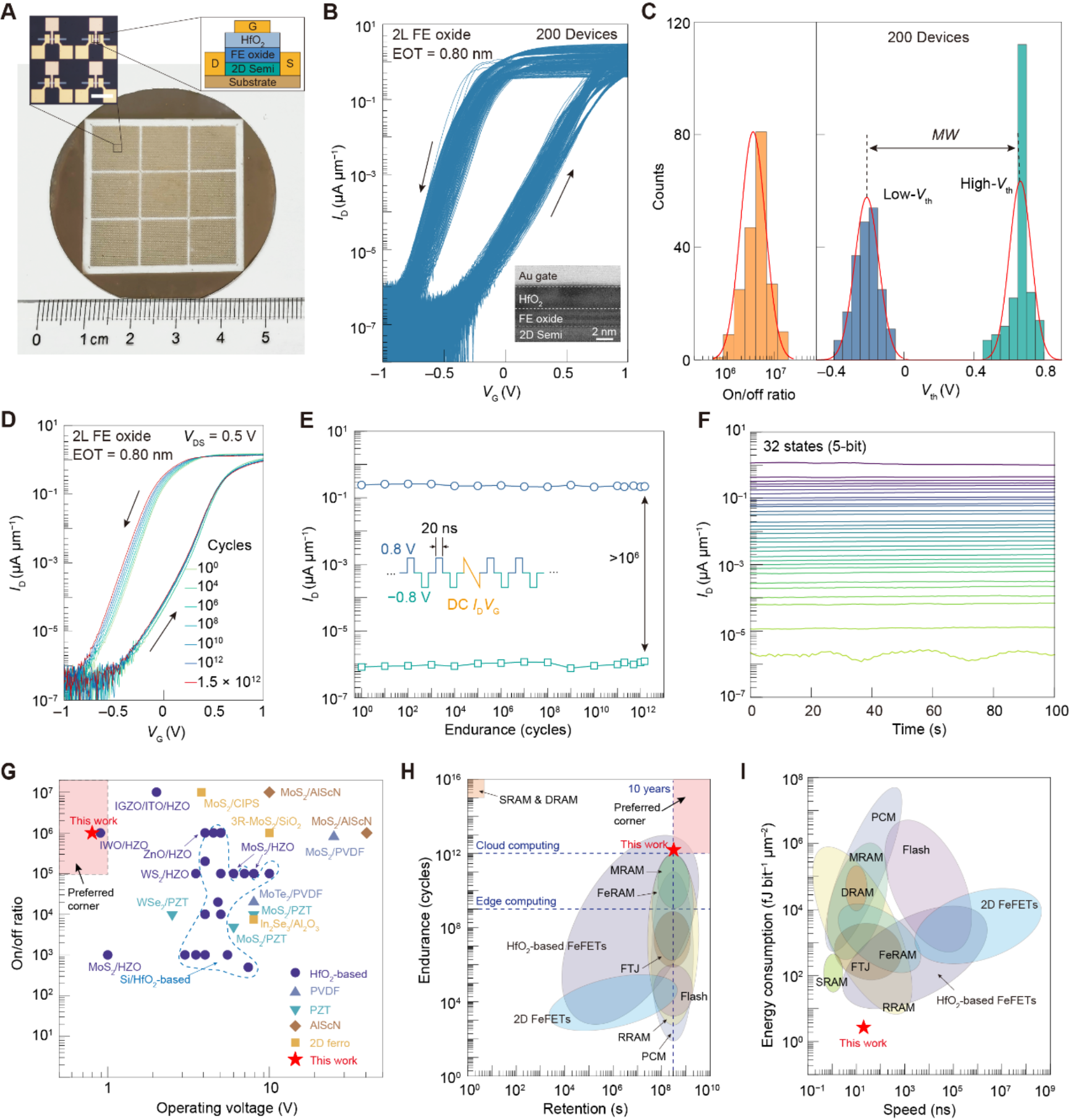

该研究工作通过原位氧化方法,构筑了原子级平整的二维铁电/半导体异质结构α-Bi2SeO5/Bi2O2Se,并成功制备了晶圆级二维铁电晶体管(FeFET)阵列(图3)。该阵列展现出优异的电学性能:器件开关比超过106,在±1 V的工作电压下具有0.9 V的回滞窗口,且器件间均一性控制在5%以内。更突出的是,借助于α-Bi2SeO5层状结构中独特的抗铁电极化疲劳Bi2O2骨架以及低缺陷的自氧化异质界面,FeFET器件在0.8 V的超低工作电压和20 ns的高速写入条件下,实现了超过1.5×1012次的循环耐久性,该指标已超越同类器件的工业最高水平,完全满足云端AI计算对可靠性的严苛要求。此外,该FeFET器件还具备超过10年的数据保持时间、32个稳定的多级存储态(5 bit)以及2.8 fJ bit−1 μm−2的超低操作能耗,能效优于其他存储体系1–2个数量级。这项工作表明,α-Bi2SeO5 能够突破传统铁电材料在保持时间与耐久性、速度与能耗之间的性能制约,为面向AI计算需求的低功耗、三维集成存算一体架构提供了极具潜力的解决方案,也为“超越摩尔”路线的发展开拓了可扩展、高可靠且兼容三维集成的二维铁电材料新路径。

图3. 二维α-Bi2SeO5/Bi2O2Se铁电晶体管器件及性能。(A)2英寸晶圆二维α-Bi2SeO5/Bi2O2Se FeFET阵列;(B)2英寸晶圆上200个FeFET的转移曲线;(C)对应(B)中器件开/关比和存储窗口统计;(D)1.5×1012次循环测试的FeFET转移曲线;(E)1.5×1012次循环测试下FeFET的开/关态电流密度统计;(F)FeFET的32个多电导态演示;(G-I)二维αBi2SeO5/Bi2O2Se FeFET与其他铁电材料及不同存储材料体系的综合性能对比。

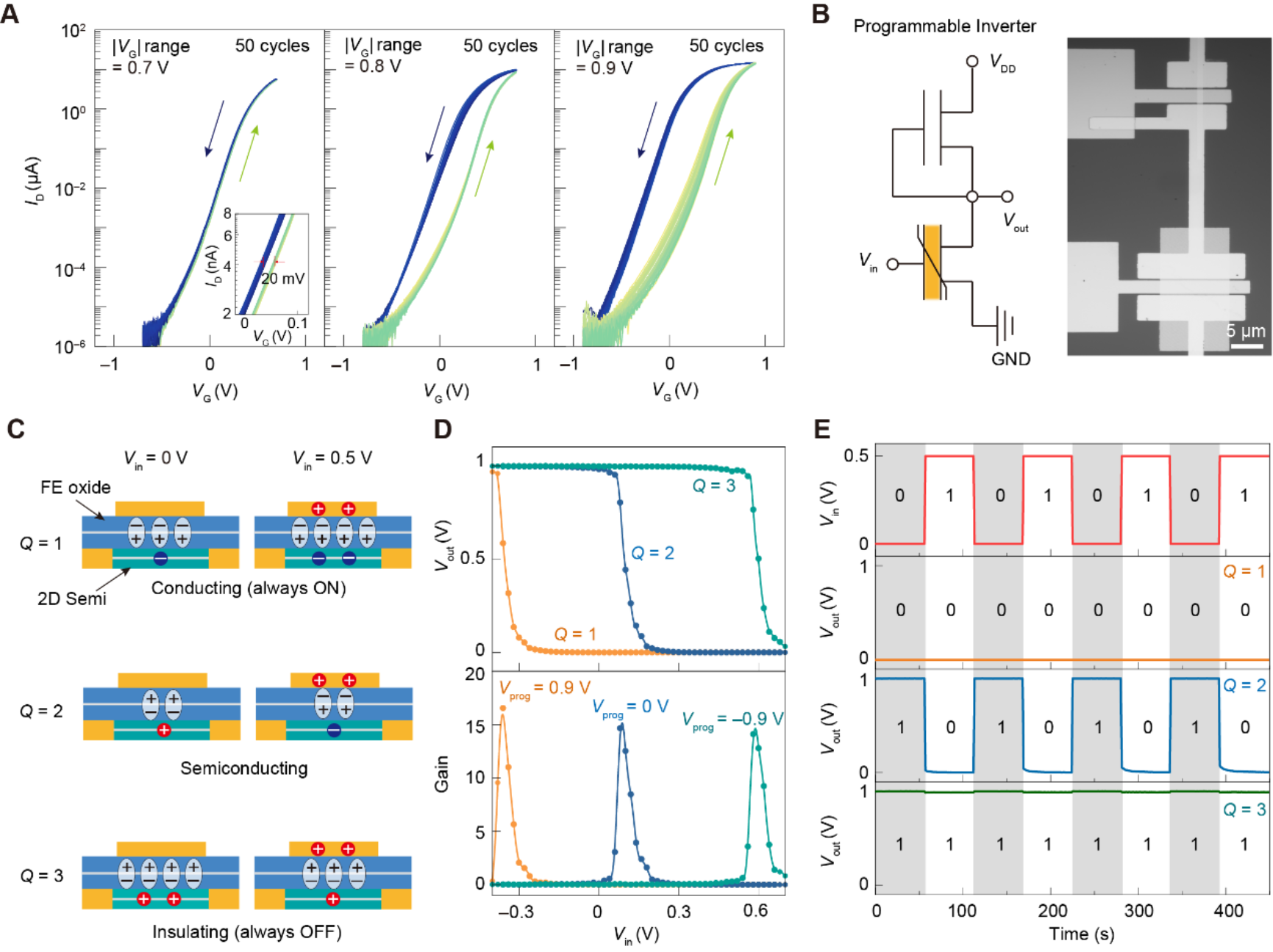

基于上述超低电压、超高耐久性的FeFET器件,该研究工作进一步构建出可动态重构的存内逻辑运算电路。该电路在CMOS常规低工作电压(<1 V)下即可实现可切换的逻辑功能,充分展示了其在下一代存算一体架构中的重要应用潜力(图4)。在未达到矫顽电场的较低栅电压下,器件展现出无回滞的高性能晶体管特性,可用作常规反相器执行逻辑运算;而当栅压超过矫顽电场时,器件可无缝切换至非易失存储状态,实现数据的长期保持。这种“一器两用”的可重构特性,显著提升了CMOS电路的设计自由度,为构建自适应、低功耗的智能计算系统奠定了关键器件基础。

图4. 低功耗二维α-Bi2SeO5/Bi2O2Se铁电晶体管基可重构的存内逻辑电路。(A)二维α-Bi2SeO5/Bi2O2Se FeFET在不同电压下的转移曲线,随着电压增加,器件从无回滞晶体管特性切换至非易失存储特性;(B)基于二维α-Bi2SeO5/Bi2O2Se FeFET的可动态重构存内逻辑运算电路;(C)用于可重构存内逻辑运算的FeFET 工作状态示意图;(D)该存内逻辑电路在不同状态下的输出特性;(E)该存内逻辑电路在三种状态下工作的循环性能。

审稿人评价认为:“该工作不仅突破了传统铁电材料的厚度微缩限制,解决了二维铁电材料的晶圆级集成难题,也为铁电二维电子学的发展开辟了新路径——尤其是,Bi2SeO5铁电层作为二维半导体Bi2O2Se的自然氧化物,具备天然的集成优势。所制备的铁电晶体管展现出优异的存储性能和高度均一性,彰显出显著的应用潜力。”“这项工作将对铁电材料和器件领域产生深远影响,为铁电二维电子学打开了大门。”

综上所述,该研究在国际上首次实现了晶圆级超薄且均匀的二维铁电氧化物薄膜制备,并实现了与高迁移率二维半导体的三维异质集成。基于该集成体系,成功研制了兼具超低工作电压与超高耐久性的铁电晶体管及可重构的存内逻辑电路,全面展示了其在未来存算一体架构中的应用潜力。

这项原创工作的核心创新与突破在于,首次报道了性能超越现有工业级铪基铁电材料的新型铋基二维铁电体系。该体系同时突破了铁电材料制备与铁电器件性能极限,不仅为发展下一代高性能、低功耗芯片技术提供了全新的材料平台与集成路径,也标志着在“超越摩尔”技术路线上实现了从材料创新到功能验证的重要跨越。

论文信息:该论文通讯作者为北京大学化学与分子工程学院彭海琳教授及团队的刘洪涛特聘副研究员,第一作者为北京大学化学与分子工程学院博雅博士后武钦慈、博士研究生李忠睿、北京大学前沿交叉科学研究院博士研究生韩秉辰、孙玮玉、北京大学物理学院博士研究生刘沁纭及北京大学化学与分子工程学院博士研究生薛骋远。该工作合作者还包括北京大学物理学院高宇南研究员和宾夕法尼亚州立大学颜丙海教授等。该工作得到了国家自然科学基金委、科技部、新基石科学基金会等项目的资助,并得到了北京大学化学与分子工程学院分子材料与纳米加工实验室(MMNL)仪器平台的支持。

论文链接:https://www.science.org/doi/10.1126/science.adz1655

排版:高杨

审核:牛林,刘志博